ASML planea aplicar ampliamente la tecnología High‑NA EUV ya el próximo año para fabricar chips con tamaños de transistores de 1,4 nm y menos.

Resumen breve

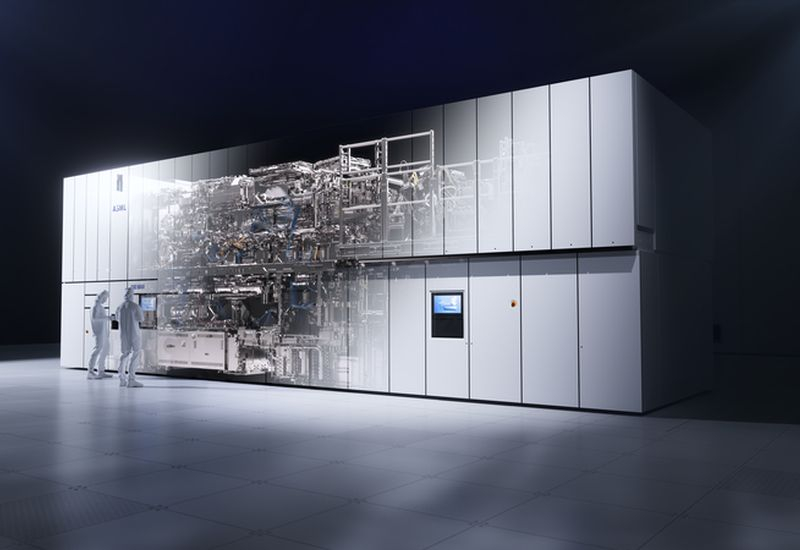

La nueva etapa de miniaturización de los circuitos integrados requiere pasar a métodos de litografía más avanzados. En los próximos dos años, la industria debe iniciar la producción de chips utilizando equipos de clase High‑NA EUV, que permiten alcanzar tamaños de hasta 8 nm en una sola pasada y abren el camino hacia procesos tecnológicos de 1,4 nm y menos de 10 nm (DRAM).

1. Capacidades tecnológicas del High‑NA EUV

Parámetro | Valor

Apertura numérica (NA) | 0,55

Tamaño mínimo por pasada | ≤ 8 nm

Procesos tecnológicos posibles | 1,4 nm (circuitos integrados), < 10 nm (DRAM)

Estas características hacen que el equipo ASML Twinscan EXE:5200B y soluciones similares sean críticos para las futuras tecnologías microelectrónicas.

2. Actores clave

Empresa | Estado de implementación | Comentario

ASML | Fabricante de High‑NA EUV | Primeros clientes: Intel, Samsung, SK Hynix

TSMC | No listo para uso masivo | Costo de un sistema – 380 mld USD; se planea abandonar los chips de 1,4 nm

Intel | En diciembre de 2023 introdujo el Twinscan EXE:5200B | Preparación para la tecnología 14A y equipos asociados

Samsung Electronics | Recibió su primer escáner en diciembre de 2023; segundo en este semestre | Planea usarlo para Exynos 2600 (2 nm) y futuros procesadores Tesla

SK Hynix | Domina el High‑NA EUV desde septiembre de 2023 | Ya usa litografía EUV estándar en DRAM (10 nm), planea usar al menos cinco capas EUV para la sexta generación

Micron Technology | Todavía no ha definido plazos | Posibles planes con High‑NA EUV

Rapidus (Japón) | Domina la tecnología de 2 nm; planea 1,4 nm en 2029 | Para 2027 debe lanzar producción masiva de chips de 2 nm en Hokkaido

3. Aspectos económicos

* El costo del equipo – un sistema High‑NA EUV cuesta alrededor de 380 mld USD.

* La transición a equipos más caros aumenta el coste de producción, lo que finalmente se refleja en los consumidores.

* Por eso los grandes fabricantes (TSMC, Rapidus) actúan con cautela y planean una implementación gradual.

4. Plazos esperados

Los nuevos escáneres litográficos ASML para la producción masiva de semiconductores avanzados comenzarán a usarse activamente entre 2027 y 2028. Hasta entonces, las empresas ajustarán gradualmente sus líneas de producción, integrando High‑NA EUV en los procesos tecnológicos existentes.

Conclusión

La transición al High‑NA EUV es el paso clave para alcanzar tamaños de hasta 1,4 nm y DRAM más compactos. Los principales actores mundiales ya han iniciado trabajos preparatorios, pero la adopción masiva se espera solo dentro de unos años debido a los altos costos y la necesidad de adaptar las cadenas de producción.

Asted Cloud

Asted Cloud

Comentarios (0)

Comparte tu opinión — por favor, sé amable y mantente en el tema.

Inicia sesión para comentar